# PL2303GE

# PL2303GE USB to Full UART IC With Integrated System-Level ESD Protection

## **USB** Interface

- Fully Compliant with USB 2.0 specification (Full-Speed Mode).

- UHCI/OHCI (USB 1.1), EHCI (USB 2.0), xHCI (USB 3.1) Host Controller Compatible.

- ±15kV High ESD HBM (Human Body Model) Protection on USB Port (4-pin):

- ±15kV IEC 61000-4-2 Air Discharge

- ±8kV IEC 61000-4-2 Contact Discharge

- Provides royalty-free USB to Virtual Com Port (VCP) drivers for Windows, Mac, Linux, and Android.

- Highly integrated USB 1.1 FS Transceiver. Integrated termination resistors and pull-up resistor to reduce PCB external components.

- Supports 256-byte OTPROM (One-Time Programmable ROM) for USB device descriptors and GPIO custom configuration. OTPROM can be programmed directly through USB port.

- Each IC has unique ID (for Serial Number).

- Supports bus-power, self-power and high-power USB device configuration.

- Supports Windows USB Selective Suspend (Remote Wakeup enabled).

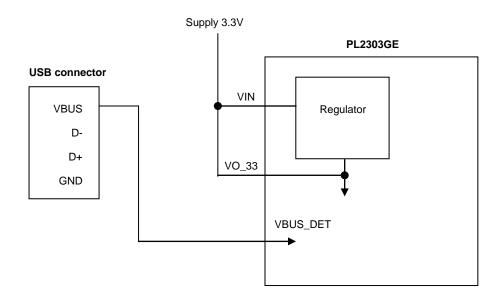

- Supports VBUS input detect function to attach USB host after VBUS is detected.

- Supports 3.3V VBUS voltage operation.

## **GPIO** Interface

- Versatile GPIO functions and routing logic provides easy to use multi-I/O functions.

- Configurable I/O pin output driving strength.

- Total 16 General Purpose I/O (GPIO) pins can be used after configured.

- Optional Clock Output to external MCU.

## UART Interface

- Supports Serial UART Interface:

- o RS232, RS422, RS485

- Flexible baud rate support up to 12Mbps

- $\circ$  5, 6, 7 or 8 data bits

- o Odd, Even, Mark, Space, None parity mode

- o One, one and a half, or two stop bits

- Hardware Flow Control (CTS/RTS and/or DSR/DTR)

- Software Flow Control (XON/XOFF)

- o Configurable Remote Wakeup Pin

- 1024-byte bi-directional data FIFO buffers (768-byte receive/256-byte transmit) for faster data throughput. Configurable in OTPROM.

- Configurable Transmit and Receive LED pins.

- Suspend Pin control for RS232 transceiver.

- UART inverted signal configurable option.

## **Battery Charger Detection**

• Supports Battery Charger (BC1.2) Detection to enable fast charging of batteries.

## Miscellaneous

- Integrated self-generated precise clock generator. External crystal is optional.

- Integrated Power-on-Reset (POR) circuit.

- Integrated 100mA 5V to 3.3V regulator that can support external components within the limit.

- Low operating power and USB suspend current.

- Wide I/O voltage range (1.8V/2.5V/3.3V/5V).

- -40°C to 85°C Operating Temperature.

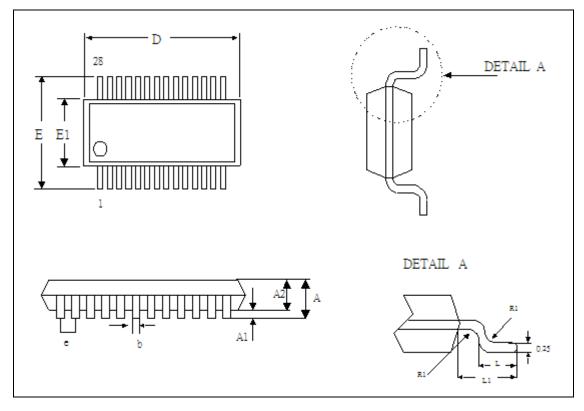

- 28-pin SSOP IC package (RoHS compliant and Pb-free Green Compound).

- Pin-compatible with PL2303HXD/PL2303EA chip (SSOP28).

# PL2303GE

# 1. **Product Applications**

- Single-chip upgrade solution for Legacy RS232 devices to USB interface

- USB to RS232/RS422/RS485 interface converters/cables/dongles/adapters

- MCU-based devices to USB host interface

- Point-of-Sale (POS) Terminals/Printers/Pole Displays

- USB Barcode/Smart Card Readers

- PC I/O Docking Station/Port Replicators

- Healthcare/Medical USB Interface Data Transfer Cable

- Serial-over-IP Wireless Solution

- Cellular/PDA USB Interface Data Transfer Cable

- GPS/Navigation USB Interface

- Industrial / Instrumentation / Automation Control USB Interface

- USB Modem / Wireless / Zigbee USB Interface

- Set-Top Box (STB) / Home Gateway USB Interface

- Battery Charger Detection for high-current and quick charging of batteries.

# 2. Royalty-Free Driver Support

- Windows 10, 8, 7, Vista, XP(Microsoft Certified WHQL Drivers)

- Windows Update Driver installation available in Windows 7 and above (32/64-bit)

- Windows Server 2003, 2008, 2008 R2, 2012, 2016

- Windows Embedded Industry, Point-of-Service (WEPOS), and POSReady

- Windows Embedded Compact, Windows Embedded CE, Windows CE

- Mac OS X

- Linux OS

- Android 3.2 and above

# 3. Ordering Information

| Chip Product Name | Package Type Ordering Part Number |                | MPQ            |

|-------------------|-----------------------------------|----------------|----------------|

| PL2303GE          |                                   | PL2303G3ZJG7P4 | 48pcs / tube   |

|                   | 28-pin SSOP                       | PL2303G3ZJG8P4 | 2000pcs / reel |

PL2303GE

PL2303GE

5. USB Logo Certification

(TBA)

# Table of Contents

| 1. | Product Applications2        |                                                      |  |  |  |  |  |

|----|------------------------------|------------------------------------------------------|--|--|--|--|--|

| 2. | Royalty-Free Driver Support2 |                                                      |  |  |  |  |  |

| 3. | Ordering Information         |                                                      |  |  |  |  |  |

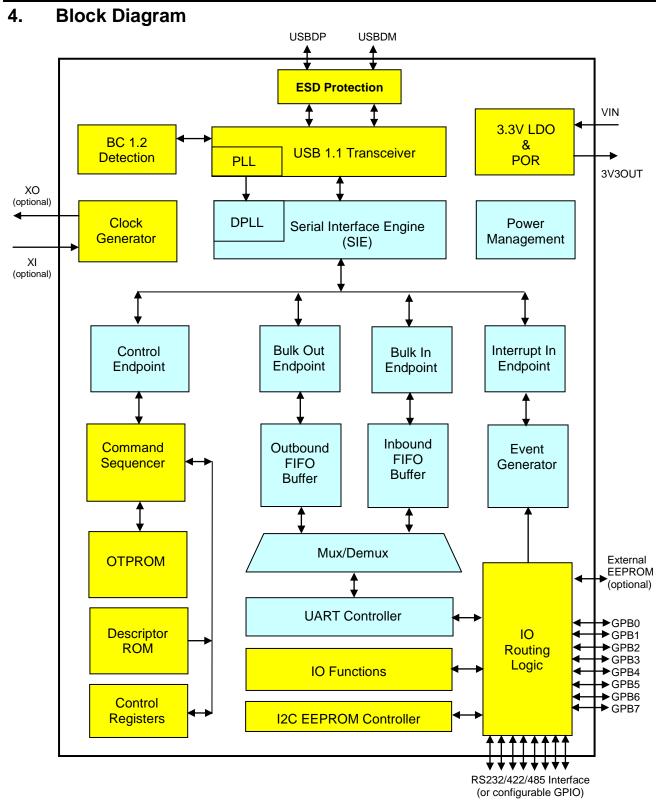

| 4. | Bloc                         | ck Diagram3                                          |  |  |  |  |  |

| 5. | USE                          | B Logo Certification4                                |  |  |  |  |  |

| 6. | Ove                          | rview9                                               |  |  |  |  |  |

|    | 6.1                          | PL2303 G-Series USB to Serial Family Product Table10 |  |  |  |  |  |

| 7. | Pin                          | Diagram and Description11                            |  |  |  |  |  |

|    | 7.1                          | SSOP28 Pin Diagram                                   |  |  |  |  |  |

|    | 7.2                          | Pin Out Description                                  |  |  |  |  |  |

|    | 7.4                          | GPIO Multi-Function Options                          |  |  |  |  |  |

| 8. | Fun                          | ctional Description16                                |  |  |  |  |  |

|    | 8.1                          | ESD Protection                                       |  |  |  |  |  |

|    | 8.2                          | BC 1.2 Detection                                     |  |  |  |  |  |

|    | 8.3                          | USB 1.1 FS Transceiver                               |  |  |  |  |  |

|    | 8.4                          | LDO Regulator16                                      |  |  |  |  |  |

|    | 8.5                          | Clock Generator                                      |  |  |  |  |  |

|    | 8.6                          | USB FS SIE16                                         |  |  |  |  |  |

|    | 8.7                          | Power Management17                                   |  |  |  |  |  |

|    | 8.8                          | Control Endpoint17                                   |  |  |  |  |  |

|    | 8.9                          | Bulk Out Endpoint17                                  |  |  |  |  |  |

|    | 8.10                         | Bulk In Endpoint17                                   |  |  |  |  |  |

|    | 8.11                         | Interrupt In Endpoint17                              |  |  |  |  |  |

|    | 8.12                         | Command Sequencer17                                  |  |  |  |  |  |

|    | 8.13                         | Outbound FIFO18                                      |  |  |  |  |  |

|    | 8.14                         | Inbound FIFO                                         |  |  |  |  |  |

|    | 8.15                         | Event Generator                                      |  |  |  |  |  |

|    | 8.16                         | Internal OTPROM18                                    |  |  |  |  |  |

|    | 8.17                         | Mux/Demux18                                          |  |  |  |  |  |

|    | 8.18                         | Descriptor ROM                                       |  |  |  |  |  |

|    | 8.19                         | UART Control                                         |  |  |  |  |  |

|     | 8.20 Control Registers                       | 19 |

|-----|----------------------------------------------|----|

|     | 8.21 IO Functions                            | 19 |

|     | 8.22 I/O Routing Logic                       | 19 |

|     | 8.23 I2C EEPROM Controller                   | 19 |

| 9.  | Chip Function Configuration                  | 20 |

|     | 9.1 USB Data Configuration                   | 20 |

|     | 9.2 UART Configuration                       | 22 |

|     | 9.3 GPIO (GPA) Configuration                 | 23 |

|     | 9.4 GPIO (GPB) Configuration                 | 25 |

|     | 9.5 Miscellaneous (MISC) Configuration       | 27 |

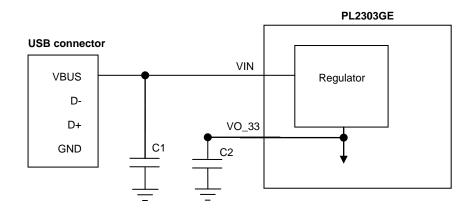

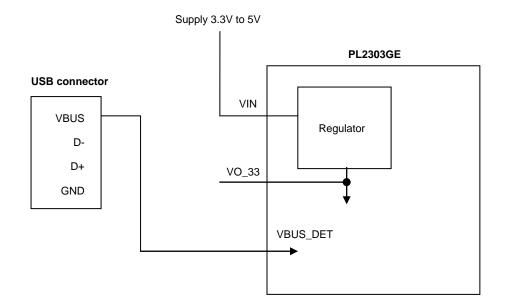

| 10. | Design Application Examples                  | 28 |

|     | 10.1 USB Bus Powered Design                  |    |

|     | 10.2 Self Powered Design                     |    |

|     | 10.3 Chip Reset Control                      |    |

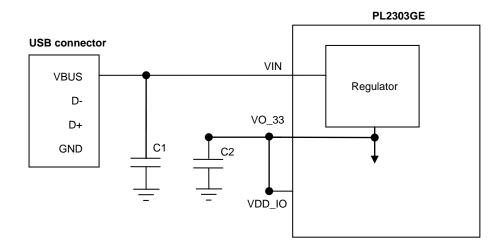

|     | 10.4 I/O Power Supply to PL2303GE            | 31 |

|     | 10.5 USB to RS232 Cable Design               |    |

|     | 10.6 USB to RS485/RS422                      |    |

|     | 10.7 Battery Charging Support                | 34 |

|     | 10.8 External I2C EEPROM Support             |    |

| 11. | DC & Temperature Characteristics             | 37 |

|     | 11.1 Absolute Maximum Ratings                |    |

|     | 11.2 DC Characteristics                      |    |

|     | 11.2.1 Operating Voltage and Suspend Current |    |

|     | 11.2.2 I/O Pins                              |    |

|     | 11.3 ESD Protection                          |    |

|     | 11.4 Temperature Characteristics             |    |

|     | 11.5 Baud Rate Characteristics               |    |

| 12. | Outline Diagram                              |    |

|     | 12.1 SSOP28 Package                          |    |

| 13. | Packing Information                          | 40 |

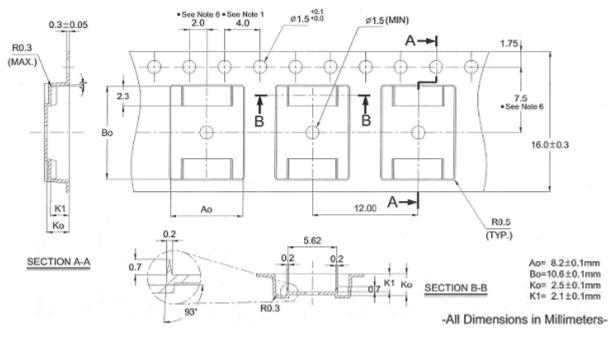

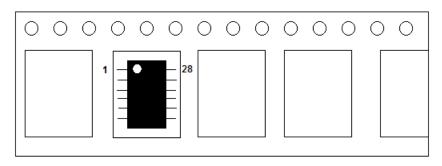

|     | 13.1 Carrier Tape (SSOP-28)                  | 40 |

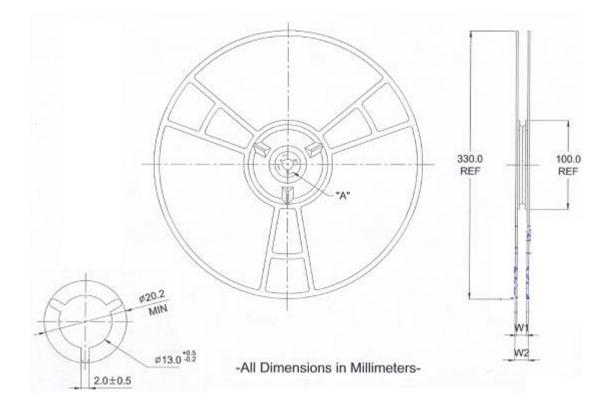

|     | 13.2 Reel Dimension                          | 41 |

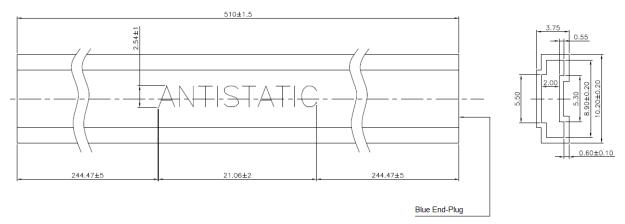

|     | 13.3 Tube Packing                            | 42 |

# List of Figures

| ïgure 4-1 PL2303GE Block Diagram3                |

|--------------------------------------------------|

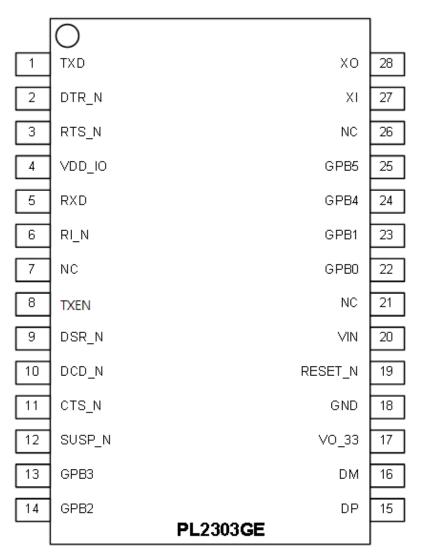

| igure 7-1 PL2303GE Pin Diagram (SSOP28)11        |

| igure 10-1 USB Bus Powered Design Example28      |

| igure 10-2a USB Self Powered Design Example 129  |

| igure 10-2b USB Self Powered Design Example 229  |

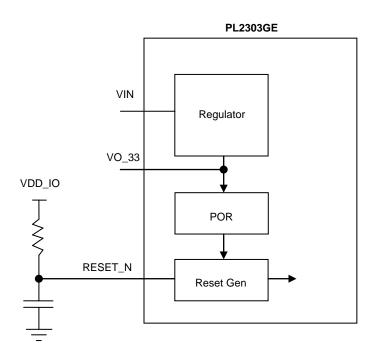

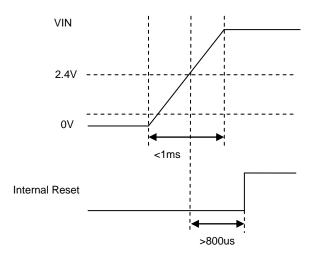

| igure 10-3a Chip Reset Control Application30     |

| igure 10-3b Chip Power Reset Timing Diagram30    |

| igure 10-4a IO Power Supply31                    |

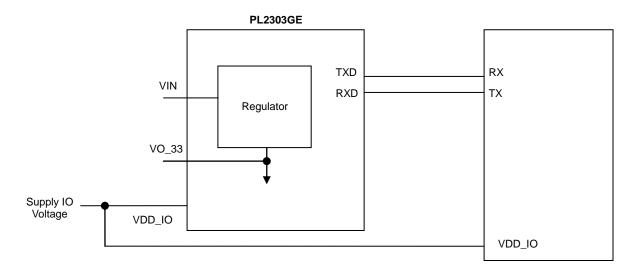

| igure 10-4b VDD_IO Voltage Supply31              |

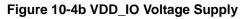

| igure 10-5 USB to RS232 Design Example32         |

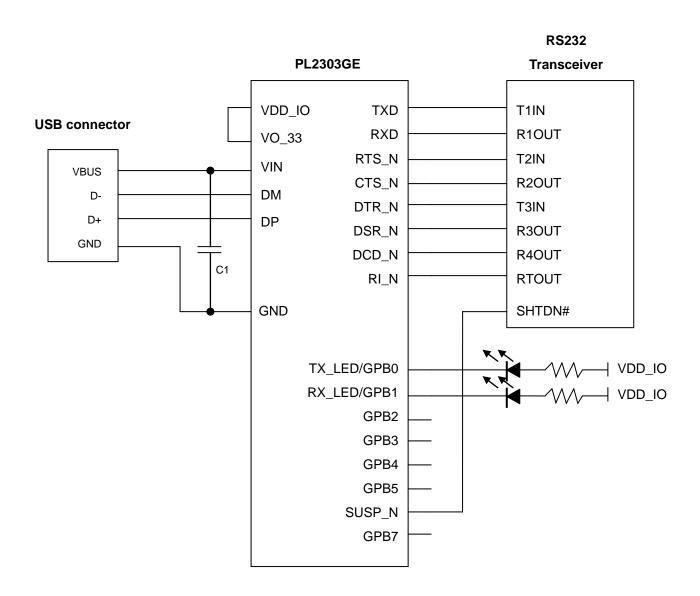

| igure 10-6 USB to RS485/422 Design Example33     |

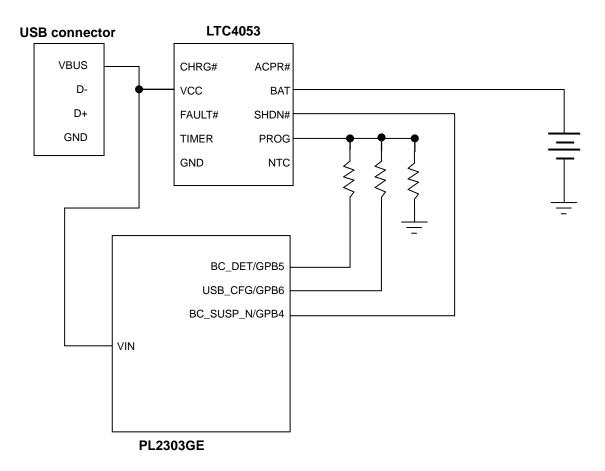

| igure 10-7a Battery Charging Design Example #134 |

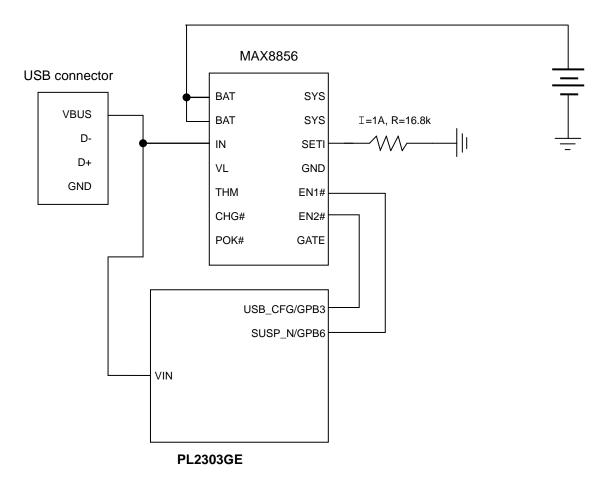

| igure 10-7b Battery Charging Design Example #235 |

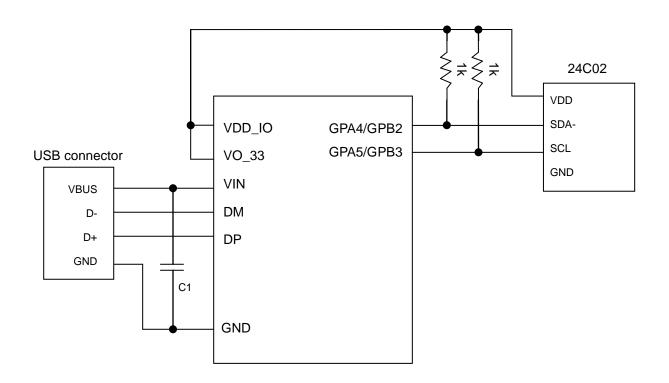

| igure 10-8 External I2C EEPROM Design Example    |

| igure 12-1 PL2303GE Outline Diagram (SSOP28)39   |

| igure 13-1a SSOP28 Carrier Tape40                |

| igure 13-1b IC Reel Placements40                 |

| igure 13-2 Reel Dimension41                      |

| igure 13-3 Tube Packing Dimension42              |

# List of Tables

| Table 7-1: USB Data Interface Pins    12                                   |

|----------------------------------------------------------------------------|

| Table 7-2: UART (Serial Port) Interface Pins12                             |

| Table 7-3: Configurable GPIO Pins – Group A (Shared with Serial Port Pins) |

| Table 7-4: Configurable GPIO Pins – Group B13                              |

| Table 7-5: Power and Ground Pins    13                                     |

| Table 7-6: Miscellaneous Pins    13                                        |

| Table 7-7: Configurable GPIO Multi-Function Pins14                         |

| Table 7-8: GPIO Multi-Function Option Descriptions    14                   |

| Table 9-1 USB Descriptor Configuration                                     |

| Table 9-2 UART Startup Configuration                                       |

| Table 9-3 GPIO (GPA Group) Configuration                                   |

| Table 9-4 GPIO (GPB Group) Configuration                                   |

| Table 9-5 Miscellaneous Configuration                                      |

| Table 11-1 Absolute Maximum Ratings                                        |

| Table 11-2a Operating Voltage and Suspend Current                          |

| Table 11-2b I/O Pins                                                       |

| Table 11-3 ESD Protection                                                  |

| Table 11-4 Temperature Characteristics    38                               |

| Table 11-5 Baud Rate Characteristics                                       |

| Table 12-1 Package Dimension                                               |

| Table 13-1 Reel Part Number Information41                                  |

## 6. Overview

The new PL2303GE chip is one of the latest G-Series IC product added to the popular PL2303 USB to Serial (UART) Bridge Controller family, replacing the PL2303EA (with ESD protection) chip. It provides an advanced full-featured single-chip bridge solution for connecting a full-duplex UART asynchronous serial interface device to any Universal Serial Bus (USB) capable host. The PL2303GE provides highly compatible USB drivers to simulate the traditional COM port (via virtual COM Port) on most operating systems allowing existing serial UART applications based on legacy COM port to easily migrate and be made USB ready.

The PL2303GE provides USB port system-level ESD (electrostatic discharge) protection that eliminates the need for external ESD protection components to minimize PCB size and save BOM costs. The PL2303GE offers ESD protection on the USB port pins up to ±15kV Human Body Model (HBM) and is according to the IEC-61000-4-2 ESD specification.

The new PL2303GE is pin-to-pin compatible with the PL2303EA chip. It also integrates an internal precise clock generator (no external crystal required), USB 1.1 transceiver, Serial Interface Engine (SIE), LDO voltage regulator, power-on- reset (POR), FIFO data buffers, and OTPROM.

The PL2303GE added several new features and enhancements:

- Integrated termination resistors and pull-up resistor to reduce PCB external components.

- New USB drivers for different OS platforms with faster performance and advanced features.

- Precise baud rate generator (up to 12Mbps).

- OTPROM can be programmed directly through USB (no high voltage generator required).

- Larger TX/RX FIFO data buffers (1024-byte).

- Up to 16 configurable GPIO pins.

- Versatile GPIO functions and routing logic (TX/RX LED, VBUS\_DET, USB\_CFG, CLK\_OUT, etc.).

- Supports 3.3V VBUS voltage operation.

- Wide I/O voltage range (1.8V/2.5V/3.3V/5V).

- Configurable I/O pin output driving strength.

- UART inverted signal configurable option.

- Unique USB Serial Number for each IC.

- Supports Battery Charger (BC1.2) Detection to enable fast charging of batteries.

The PL2303GE is designed to support a wide-range of serial application domain including mobile, embedded, industrial, consumer, healthcare, navigation, and wearable solutions in mind. It provides a small footprint that could easily fit in to any connectors and handheld devices. With very small power consumption in either operating or suspend mode, the PL2303GE is perfect for bus powered operation with plenty of power left for the attached devices. Flexible signal level requirement on the RS232-like serial port side also allows the PL2303GE to connect directly to any 5V~1.8V range devices.

### 6.1 PL2303 G-Series USB to Serial Family Product Table

Prolific's new PL2303 G-series USB to Serial family product line offers a variety of new advanced features for USB serial interface product design. The PL2303 G-series are redesigned to provide accurate and flexible baud rate support as well as plenty of I/O functions that can be easily configured in OTPROM memory.

| PL2303 G-Series USB to Serial (UART) Family Product Line |                                             |                                             |                                              |                                                 |                                            |  |  |

|----------------------------------------------------------|---------------------------------------------|---------------------------------------------|----------------------------------------------|-------------------------------------------------|--------------------------------------------|--|--|

| Product                                                  | PL2303GC                                    | PL2303GS                                    | PL2303GE                                     | PL2303GT                                        | PL2303GL                                   |  |  |

| Description                                              | USB to Full UART<br>(Integrated Clock)      | USB to Full UART<br>(Integrated Clock)      | USB to Full UART<br>(High ESD<br>Protection) | USB to RS232<br>(Internal RS232<br>Transceiver) | USB to Basic<br>UART<br>(Low-Pin<br>Count) |  |  |

| Packages                                                 | SSOP28<br>QFN24                             | SSOP16<br>QFN16                             | SSOP28                                       | SSOP28                                          | SOP8<br>UDFN8                              |  |  |

| UART Interface                                           | RS232<br>RS422/RS485                        | RS232<br>RS422/RS485                        | RS232<br>RS422/RS485                         | RS232 Only                                      | RS232<br>(TX-RX Only)                      |  |  |

| Max. Data Rates                                          | 12Mbps                                      | 12Mbps                                      | 12Mbps                                       | 1Mbps                                           | 115200bps                                  |  |  |

| Dedicated GPIO<br>Pins                                   | 6                                           | 0                                           | 6                                            | 4                                               | 0                                          |  |  |

| Shared GPIO (with UART pins)                             | 9                                           | 9                                           | 9                                            | 0                                               | 0                                          |  |  |

| Clocking                                                 | Internal <sup>1</sup>                       | Internal                                    | Internal <sup>1</sup>                        | Internal                                        | Internal                                   |  |  |

| OTPROM <sup>2</sup>                                      | USB Data +<br>Configurable<br>GPIO Function | USB Data +<br>Configurable<br>GPIO Function | USB Data +<br>Configurable<br>GPIO Function  | USB Data +<br>Configurable<br>GPIO Function     | USB Data                                   |  |  |

| External EEPROM<br>Option                                | YES <sup>3</sup>                            | YES <sup>3</sup>                            | YES <sup>3</sup>                             | YES <sup>3</sup>                                | NO                                         |  |  |

| Android OS<br>Support                                    | YES                                         | YES                                         | YES                                          | YES                                             | YES                                        |  |  |

| Configurable Data<br>Buffer <sup>4</sup>                 | 768-byte (RX)<br>256-byte (TX)              | 768-byte (RX)<br>256-byte (TX)              | 768-byte (RX)<br>256-byte (TX)               | 768-byte (RX)<br>256-byte (TX)                  | 768-byte (RX)<br>256-byte (TX)             |  |  |

| Battery Charger<br>Detection Option                      | YES                                         | YES                                         | YES                                          | No                                              | No                                         |  |  |

| I/O Voltage Range                                        | I/O levels from<br>1.8V to 5V               | I/O levels from<br>1.8V to 5V               | I/O levels from<br>1.8V to 5V                | 3.3V                                            | I/O levels from<br>1.8V to 5V              |  |  |

| Pin Compatible                                           | PL2303HXD<br>(SSOP28 only)                  | New design                                  | PL2303EA                                     | PL2303RA                                        | PL2303SA<br>(SOP8 only)                    |  |  |

<sup>1</sup> – Also supports external crystal clock source to bypass internal clock.

$^{2}$  – OTPROM allows setting the USB data descriptors. Also allows setting of multi-function GPIO options.

<sup>3</sup> – External EEPROM (when enabled in OTPROM) will override OTPROM settings.

<sup>4</sup> – TX/RX data buffers are configurable in OTPROM (PL2303GC, PL2303GS, and PL2303GE); or by driver customization.

# 7. Pin Diagram and Description

# 7.1 SSOP28 Pin Diagram

Figure 7-1 PL2303GE Pin Diagram (SSOP28)

# 7.2 Pin Out Description

#### Table 7-1: USB Data Interface Pins

| Pin Name | SSOP28<br>Pin No. | Туре | Description                     |

|----------|-------------------|------|---------------------------------|

| DP       | 15                | I/O  | USB Port Data Plus (D+) Signal  |

| DM       | 16                | I/O  | USB Port Data Minus (D-) Signal |

#### Table 7-2: UART (Serial Port) Interface Pins

| Pin Name | SSOP28<br>Pin No. | Туре   | Description                                               |

|----------|-------------------|--------|-----------------------------------------------------------|

| TXD      | 1                 | Output | Serial Port: Transmitted Data Output                      |

| DTR_N    | 2                 | Output | Serial Port: Data Terminal Ready Control Output           |

| RTS_N    | 3                 | Output | Serial Port: Request To Send Control Output               |

| RXD      | 5                 | Input  | Serial Port: Received Data Input                          |

| RI_N     | 6                 | Input  | Serial Port: Ring Indicator (Remote Wakeup) Control Input |

| DSR_N    | 9                 | Input  | Serial Port: Data Set Ready Control Input                 |

| DCD_N    | 10                | Input  | Serial Port: Data Carrier Detect Control Input            |

| CTS_N    | 11                | Input  | Serial Port: Clear To Send Control Input                  |

## Table 7-3: Configurable GPIO Pins – Group A (Shared with Serial Port Pins)

| Pin Name | SSOP28<br>Pin No. | Туре                                     | Description                                      |

|----------|-------------------|------------------------------------------|--------------------------------------------------|

| GPA0     | 1                 | I/O                                      | Configurable GPIO Pin. (see Section 7.4)         |

| GPAU     | Ι                 | 1/0                                      | Factory default is TXD serial port output pin.   |

| GPA1     | F                 | I/O                                      | Configurable GPIO Pin. (see Section 7.4)         |

| GPAT     | 5                 | 1/0                                      | Factory default is RXD serial port input pin.    |

| GPA2     | 2                 | I/O                                      | Configurable GPIO Pin. (see Section 7.4)         |

| GPAZ     | 3                 | 1/0                                      | Factory default is RTS_N serial port output pin. |

|          | 44                | I/O                                      | Configurable GPIO Pin. (see Section 7.4)         |

| GPA3     | 11                |                                          | Factory default is CTS_N serial port input pin.  |

|          | 0                 |                                          | Configurable GPIO Pin. (see Section 7.4)         |

| GPA4     | 2                 | I/O                                      | Factory default is DTR_N serial port output pin. |

|          | 0                 | I/O                                      | Configurable GPIO Pin. (see Section 7.4)         |

| GPA5     | 9                 |                                          | Factory default is DSR_N serial port input pin.  |

| 0.51.0   |                   | Configurable GPIO Pin. (see Section 7.4) |                                                  |

| GPA6     | 10                | I/O                                      | Factory default is DCD_N serial port input pin.  |

| 0.54.5   | C                 | 1/0                                      | Configurable GPIO Pin. (see Section 7.4)         |

| GPA7     | GPA7 6            | 6 I/O                                    | Factory default is RI_N serial port input pin.   |

#### Table 7-4: Configurable GPIO Pins – Group B

| Pin Name | SSOP28<br>Pin No. | Туре                                     | Description                              |

|----------|-------------------|------------------------------------------|------------------------------------------|

| GPB0     | 22                | I/O                                      | Configurable GPIO Pin. (see Section 7.4) |

| GPB1     | 23                | I/O                                      | Configurable GPIO Pin. (see Section 7.4) |

| GPB2     | 14                | I/O                                      | Configurable GPIO Pin. (see Section 7.4) |

| GPB3     | 13                | I/O                                      | Configurable GPIO Pin. (see Section 7.4) |

| GPB4     | 24                | I/O                                      | Configurable GPIO Pin. (see Section 7.4) |

| GPB5     | 25                | I/O                                      | Configurable GPIO Pin. (see Section 7.4) |

| GPB6 12  | 1/0               | Configurable GPIO Pin. (see Section 7.4) |                                          |

|          | 12                | I/O                                      | Factory default is SUSP_N output pin.    |

| GPB7 8   | 0                 | 8 I/O                                    | Configurable GPIO Pin. (see Section 7.4) |

|          | 0                 |                                          | Factory default is TXEN output pin.      |

#### Table 7-5: Power and Ground Pins

| Pin Name | SSOP28<br>Pin No. | Туре  | Description                                                                                          |

|----------|-------------------|-------|------------------------------------------------------------------------------------------------------|

| VDD_IO   | 4                 | Power | +1.8V to +5V I/O signal power input pin.                                                             |

| VO_33    | 17                | Power | +3.3V output power from integrated LDO regulator. For self-powered design, supply +3.3V to this pin. |

| GND      | 18                | Power | Ground                                                                                               |

| VIN      | 20                | Power | USB port VBUS input power supply.<br>For self-powered design, supply +3.3V to this pin.              |

#### Table 7-6: Miscellaneous Pins

| Pin Name | SSOP28<br>Pin No. | Туре   | Description                                                                                                                                               |

|----------|-------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| SUSP_N   | 12                | Output | Active low Shutdown control pin. Can be used to shutdown external RS232 transceiver.                                                                      |

| RESET_N  | 19                | Input  | Active low Reset pin. Can be used by external device to reset the PL2303GC.<br>NOTE: This pin has internal pull-high. It can be pull up to VIN or VDD_IO. |

| XI       | 27                | Input  | Optional. 12MHz crystal oscillator input.<br>If not used, leave pin floating.                                                                             |

| хо       | 28                | Output | Optional. 12MHz crystal oscillator output.<br>If not used, leave pin floating.                                                                            |

| NC       | 7, 21, 26         | NC     | No internal connection. Leave floating.                                                                                                                   |

## 7.4 GPIO Multi-Function Options

The PL2303GE chip provides a total of 16 configurable GPIO (General Purpose I/O) pins. The pins are grouped into GPA and GPB set of pins. The table below shows the possible functions that can be configured for each GPIO pin. These special functions can be easily configured in the OTPROM of the PL2303GE or to an external I2C EEPROM using the Prolific OTPROM/EEPROM software tool. When these pins are configured as standard GPIO pins, customers can refer to the Prolific GPIO SDK (software development kit) to develop software to control the GPIO pins for customer application desired functions.

| GPIO | SSOP28  | Factory Default |            | Configurable Options (using OTPROM Tool) |           |          |        |  |  |  |

|------|---------|-----------------|------------|------------------------------------------|-----------|----------|--------|--|--|--|

|      | Pin No. |                 |            |                                          |           |          |        |  |  |  |

| GPA0 | 1       | TXD             |            |                                          |           |          |        |  |  |  |

| GPA1 | 5       | RXD             |            |                                          |           |          |        |  |  |  |

| GPA2 | 3       | RTS             | TX_LED     | CLK_OUT                                  | SUSP_N    | USB_CFG  | TXEN   |  |  |  |

| GPA3 | 11      | CTS             | RX_LED     | TRX_LED                                  | WAKEUP    | VBUS_DET | BC_DET |  |  |  |

| GPA4 | 2       | DTR             | TX_LED     | CLK_OUT                                  | USB_CFG   | EE_SDA   |        |  |  |  |

| GPA5 | 9       | DSR             | RX_LED     | TRX_LED                                  | BC_SUSP_N | EE_SCL   |        |  |  |  |

| GPA6 | 10      | DCD             | VBUS_DET   | BC_DET                                   | TXEN      |          |        |  |  |  |

| GPA7 | 6       | RI (WAKEUP)     |            |                                          |           |          |        |  |  |  |

| GPB0 | 22      | GPIO Input Pin  | TX_LED     | CLK_OUT                                  |           |          |        |  |  |  |

| GPB1 | 23      | GPIO Input Pin  | RX_LED     | TRX_LED                                  |           |          |        |  |  |  |

| GPB2 | 14      | GPIO Input Pin  | VBUS_DET   | EE_SDA                                   |           |          |        |  |  |  |

| GPB3 | 13      | GPIO Input Pin  | USB_CFG    | EE_SCL                                   |           |          |        |  |  |  |

| GPB4 | 24      | GPIO Input Pin  | CLK_OUT    | BC_SUSP_N                                |           |          |        |  |  |  |

| GPB5 | 25      | GPIO Input Pin  | BC_DET     |                                          |           |          |        |  |  |  |

| GPB6 | 12      | SUSP_N          | USB_CFG    | WAKEUP                                   | CLK_OUT   |          |        |  |  |  |

| GPB7 | 8       | TXEN Pin        | GPIO Input |                                          |           |          |        |  |  |  |

| Table 7-7: | Configurable |           | ulti-Eurotion | Dinc |

|------------|--------------|-----------|---------------|------|

| Table 7-7: | Configurable | GPIO IVIL | liti-Function | PINS |

#### Table 7-8: GPIO Multi-Function Option Descriptions

| GPIO<br>Function | SSOP28<br>GPIO Pins                            | Туре   | Description                  |

|------------------|------------------------------------------------|--------|------------------------------|

| TX_LED           | GPA2 (Pin 3)<br>GPA4 (Pin 2)<br>GPB0 (Pin 22)  | Output | Serial Port: TXD Access LED. |

| RX_LED           | GPA3 (Pin 11)<br>GPA5 (Pin 9)<br>GPB1 (Pin 23) | Output | Serial Port: RXD Access LED. |

| TOVICO    | GPA3 (Pin 11)                 |         |                                                                                                                       |  |  |  |  |

|-----------|-------------------------------|---------|-----------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| TRX_LED   | GPA5 (Pin 9)                  | Output  | Serial Port: TXD and RXD Access LED.                                                                                  |  |  |  |  |

|           | GPB1 (Pin 23)                 |         |                                                                                                                       |  |  |  |  |

|           | GPA3 (Pin 11)                 |         | When this signing set to VIDUO, DET mode the device will get                                                          |  |  |  |  |

| VBUS_DET  | GPA6 (Pin 10)                 | Input   | When this pin is set to VBUS_DET mode, the device will not attach to USB until VBUS_DET input pin goes to high level. |  |  |  |  |

| VB03_DE1  | GPB2 (Pin 14)                 | input   | There must be only one pin configured as VBUS_DET pin.                                                                |  |  |  |  |

|           | GPB7 (Pin 8)                  |         |                                                                                                                       |  |  |  |  |

|           | GPA2 (Pin 3)                  |         |                                                                                                                       |  |  |  |  |

|           | GPA4 (Pin 2)                  |         | When device is attached to USB port and configured by USB                                                             |  |  |  |  |

| USB_CFG   | GPB3 (Pin 13)                 | Output  | host, this USB_CFG pin will output to high level. This pin can                                                        |  |  |  |  |

|           | GPB6 (Pin 12)                 |         | be used to enable system function after USB is configured.                                                            |  |  |  |  |

|           | GPA2 (Pin 3)                  |         |                                                                                                                       |  |  |  |  |

| TXEN      | GPA6 (Pin 10)                 | Output  | Transmit Data Enable Pin can be used to enable                                                                        |  |  |  |  |

|           | GPB7 (Pin 8)                  | •       | RS485/RS422 transceiver when data is being transmitted.                                                               |  |  |  |  |

|           | . ,                           |         | Active low Shutdown control pin. This pin has two options to                                                          |  |  |  |  |

|           |                               |         | choose. One is to indicate chip suspend state by USB bus                                                              |  |  |  |  |

| SUSP_N    | GPA2 (Pin 3)                  | Output  | state. The other option (factory default) is to indicate chip                                                         |  |  |  |  |

|           | GPB6 (Pin 12)                 |         | un-configured state and chip suspend state. These two                                                                 |  |  |  |  |

|           |                               |         | options can be configured in OTPROM or EEPROM.                                                                        |  |  |  |  |

|           | GPA3 (Pin 11)                 |         | The remote wakeup function is to wake up chip from                                                                    |  |  |  |  |

| WAKEUP    | GPA7 (Pin 6)                  | Input   | suspended state when this pin toggle in suspend state. There                                                          |  |  |  |  |

|           | GPB6 (Pin 12)                 |         | must be only one pin configured as WAKEUP pin. The factory default is RI (GPA7) pin.                                  |  |  |  |  |

|           | GPA2 (Din 11)                 |         |                                                                                                                       |  |  |  |  |

| BC DET    | GPA3 (Pin 11)                 | Quitout | Battery Charge Detect pin. This active high pin indicates BC                                                          |  |  |  |  |

| BC_DET    | GPA6 (Pin 10)                 | Output  | 1.2 DCP/CDP is detected.                                                                                              |  |  |  |  |

|           | GPB5 (Pin 25)                 |         |                                                                                                                       |  |  |  |  |

|           | GPA5 (Pin 9)                  | Quitout | This pin has same function as SUSP_N except this pin will be                                                          |  |  |  |  |

| BC_SUSP_N | GPB4 (Pin 24)                 | Output  | forced inactive in chip suspend state when BC 1.2 DCP/CDP is detected.                                                |  |  |  |  |

|           | GPA2 (Pin 3)                  |         |                                                                                                                       |  |  |  |  |

|           | GPA2 (Pin 3)<br>GPA4 (Pin 2)  |         |                                                                                                                       |  |  |  |  |

| CLK_OUT   | GPA4 (Pin 2)<br>GPB0 (Pin 22) | Outout  | This pin can generate clock output up to 12MHz. Clock rates<br>can be configured in OTPROM/EEPROM or customized       |  |  |  |  |

|           | , , ,                         | Output  | driver.                                                                                                               |  |  |  |  |

|           | GPB4 (Pin 24)                 |         |                                                                                                                       |  |  |  |  |

|           | GPB6 (Pin 12)                 |         |                                                                                                                       |  |  |  |  |

| EE_SDA    | GPA4 (Pin 2)                  | Input/  | External I2C EEPROM interface serial data signal.                                                                     |  |  |  |  |

|           | GPB2 (Pin 14)                 | Output  |                                                                                                                       |  |  |  |  |

| EE_SCL    | GPA5 (Pin 9)                  | Input/  | External I2C EEPROM interface serial clock signal.                                                                    |  |  |  |  |

|           | GPB3 (Pin 13)                 | Output  |                                                                                                                       |  |  |  |  |

# 8. Functional Description

This section details the functional block diagram description of the PL2303GE.

### 8.1 ESD Protection

The PL2303GE provides USB port system-level ESD (electrostatic discharge) protection that eliminates the need for external ESD protection components to minimize PCB size and save BOM costs. The PL2303GE offers ESD protection on the USB port pins up to ±15kV Human Body Model (HBM) and is according to the IEC-61000-4-2 ESD specification.

#### 8.2 BC 1.2 Detection

This function is used to detect VBUS power supply capability of USB host port and provides charging control to battery charging IC. This function is enabled in OTPROM by setting GPIO pin to BC\_DET option. This pin will indicate if BC 1.2 DCP/CDP is detected when device is attached to the USB port. The external battery charging IC uses the USB\_CFG and SUSP\_N signal pins to control its charging current support or the BC\_DET signal pin to enable fast charging current mode.

#### 8.3 USB 1.1 FS Transceiver

The USB Transceiver provides the USB full-speed electrical signal requirements and USB physical interface (DP/DM). This block also includes one precise internal oscillator for PLL. The PLL provides the clock to other logic functions. This block also includes the internal USB series termination resistors on the USB data lines and pull-up resistor for the DP signal.

#### 8.4 LDO Regulator

This block is the 5V to 3.3V LDO regulator to power and drive the USB transceiver. It also includes 3.3V brownout detection output signals that will be used by digital circuit to reset the chip. The LDO 5V to 3.3V can supply 100mA for chip internal and external components.

#### 8.5 Clock Generator

The clock generator module generates the 48MHz and 12MHz reference clock signals for internal chip logic. The internal clocks will be stopped while in suspend state.

#### 8.6 USB FS SIE

The USB Full-Speed Serial Interface Engine (SIE) block performs the processing of USB DP/DM signals. It translates the internal parallel data to serial data and outputs to USB FS transceiver to generate

external USB DP/DM signals timing. It also translates external USB DP/DM signals pass through USB FS transceiver to parallel data for internal circuit. This block supports USB packet decoding and encoding. It also generates and check packet CRC, bit stuffing, SYNC and EOP frame signal. The DPLL module will use the internal 48MHz clock to synchronize external DP/DM transitions to generate 12MHz clock for USB interface related circuit.

## 8.7 Power Management

This module will monitor the USB attachment and DP/DM signals state to create reset state, running state, suspend state, wakeup state, etc.

#### 8.8 Control Endpoint

The Control Endpoint module handles control endpoint packet transfer protocols such as SETUP packet, DATA packet and return status packet.

## 8.9 Bulk Out Endpoint

The Bulk Out Endpoint module handles bulk-out endpoint packet transfer protocols such as DATA packet and return status packet. It also transfers USB host bulk-out data to chip outbound FIFO.

#### 8.10 Bulk In Endpoint

The Bulk In Endpoint module handles bulk-in endpoint packet transfer protocols such as DATA packet and return status packet. It also transfers data inside the chip inbound FIFO to USB host through bulk-in DATA packet.

## 8.11 Interrupt In Endpoint

The Interrupt In Endpoint module handles interrupt-in endpoint packet transfer protocols such as DATA packet and return status packet. It transfers interrupt data generated inside the chip to USB host through interrupt-in DATA packet.

#### 8.12 Command Sequencer

This module handles the USB standard requests and vendor requests. It dispatches control signals to relative peripheral modules and gather information from peripheral modules. When it received USB standard request commands, it may check ROM data or data latched from OTP and return them to USB host. When vendor requests are received, it dispatches to peripherals to set or get something.

## 8.13 Outbound FIFO

This buffer receives data from Bulk Out Endpoint and provides data to peripheral modules. It handles read and write pointers and calculate full and empty conditions. There are also near empty threshold check to notify peripheral module that FIFO is going to empty.

### 8.14 Inbound FIFO

This buffer receives data from peripheral modules and provides data to Bulk In Endpoint. It handles read and write pointers and calculate full and empty conditions. There are also near full threshold check to notify peripheral module that FIFO is going to full.

#### 8.15 Event Generator

This module provides interrupt data to Interrupt In Endpoint. This module senses interrupt event toggle from UART peripheral and GPIO module.

#### 8.16 Internal OTPROM

The OTPROM (One-Time Programming Read-Only Memory) is used to store chip function settings, GPIO pin function setting and USB descriptor related data. A one-time programming user area of the memory is available to allow customization of settings. The user area of the PL2303GE OTPROM can now be easily programmed using the Prolific OTPROM software through USB port without any additional voltage converter requirement. Refer to Section 9.0 for more information on the OTPROM configuration settings.

#### 8.17 Mux/Demux

This module is designed to pass data between FIFO and UART peripheral module.

#### 8.18 Descriptor ROM

This block contains the USB descriptor data for returning to USB host.

#### 8.19 UART Control

The UART Control module handles the data transfer according to RS232 format and interface. Full set flow control is implemented including RTS/CTS, DTR/DSR and software flow control. Flow control circuit will check FIFO near full or near empty status to activate flow control signals. This module includes a precise baud rate generator that can generate baud rates up to 12Mbps. The baud rate is set from USB command.

### 8.20 Control Registers

The Control Registers module contains the chip control registers read and set, and initially loads from OTPROM. USB host will use USB vendor command to read and write control registers to set chip function.

## 8.21 IO Functions

The IO Functions block implements generic GPIO function and many configurable I/O functions such as TX access LED and RX access LED features, clock output features, and others (see Section 6.4).

## 8.22 I/O Routing Logic

The PL2303GE has many versatile I/O functions. Each GPIO pin is provided with multiple functions that can be configured in the OTPROM. This module multiplexes I/O functions to different chip I/O pins. It also handles I/O pin polarity, open-drain, pull-up/pull-down, and I/O pin drive capability functions.

## 8.23 I2C EEPROM Controller

The I2C EEPROM Controller provides an optional alternative solution to the OTPROM that allows an external I2C EEPROM to be attached through GPIO pins 2 and 9 (GPA4/GPA5); or pins 14 and 13 (GPB2/GPB3) for the SDA and SCL interface. Using the PL2303G OTPROM/EEPROM Writer program, customer can also write the chip function settings, GPIO pin function settings, and USB descriptor related data to external I2C EEPROM. The advantage of using an external EEPROM is that it can be written several times. The Prolific OTPROM/EEPROM software works by plugging the device through USB port without any additional voltage converter requirement. Refer to Section 9.0 for more information on the OTPROM/EEPROM configuration settings.

# 9. Chip Function Configuration

The default configuration descriptors are stored in the chip internal memory which will be loaded during power-on reset or USB bus reset whenever OTPROM is empty. Several of the USB and configuration descriptors could be modified and programmed one-time into the chip's OTPROM using the PL2303GE OTPROM/EEPROM Writer utility program. These descriptors include Vendor ID, Product ID, Serial Number, Product String, UART settings, GPIO configurations, and other configuration descriptors. The PL2303GE chip also provides an option to use an external I2C EEPROM to write the configurations several times.

## 9.1 USB Data Configuration

| USB UART   GPIO_A   GPIO_B   MISC                                                                                                                                                                                                                                                                                                                                               |                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| OTPROM / External EEPROM<br>© Use OTPROM(Space) : 1<br>© Enable Ext. EEPROM, GPA5:SCL, GPA4:SDA<br>© Enable Ext. EEPROM, GPB3:SCL, GPB2:SDA                                                                                                                                                                                                                                     | Fixed COM Port Number<br>Enable<br>COM 3  Com state MS+PS+SN |

| Device Descriptor       Configuration descriptor         Vendor ID (VID) 0x       0678         Product ID (PID) 0x       23E3         Configuration descriptor       Oevice Power mode         Oself-powered       Bus-powered(100mA)         Bus-powered(500mA)       Max Power: 100         Max Power:       100         String Length: 45 / 90 (Max) : MS: 24, PS: 21, SN: 0 |                                                              |

| Manufacturer String       Prolific Technology Inc.         Product String       USB-Serial Controller         C       Disable Serial Number         Image: Control of the serial Number ID       UNIQ_ID 0x:         C       Custom Serial Number         Prefix       :         Number (8                                                                                      | Enable PSDM                                                  |

| C Auto SN(+1) +                                                                                                                                                                                                                                                                                                                                                                 |                                                              |

#### Table 9-1 USB Descriptor Configuration

| Descriptors       | Default Value                                                                                                                                      | Description                                                                                                                                                                                                                                                            |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   |                                                                                                                                                    | This field allows writing the chip configuration settings either into the OTPROM or to an external EEPROM.                                                                                                                                                             |

| OTBBOM / External | OTPROM / External<br>EEPROM<br>Use OTPROM<br>Use OTPROM<br>• Enable Ext.<br>this option of<br>EEPROM at<br>PL2303GE.<br>EEPROM at<br>• Enable Ext. | <ul> <li>Use OTPROM – this option will write the new<br/>settings into the chip's OTPROM. The OTPROM<br/>can only be written once. If the Space box<br/>denotes a 1, it means it can be written.</li> </ul>                                                            |

|                   |                                                                                                                                                    | <ul> <li>Enable Ext. EEPROM (GPA5:SCL, GPA4:SDA) –<br/>this option can be used if there is an external I2C<br/>EEPROM attached to pins GPA5 and GPA4 of<br/>PL2303GE. Settings will be written to the external<br/>EEPROM and can be written several times.</li> </ul> |

|                   |                                                                                                                                                    | • Enable Ext. EEPROM (GPB3:SCL, GPB2:SDA) – this option can be used if there is an external I2C                                                                                                                                                                        |

|                                              |                                   | EEPROM attached to pins GPB3 and GPB2 of<br>PL2303GE. Settings will be written to the external<br>EEPROM and can be written several times.<br>NOTE: PL2303GE chip can only allow a one-time<br>switch from OTPROM to Ext EEPROM or vice-versa.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|----------------------------------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Vendor ID (VID)                              | 067B (hex)                        | USB unique Vendor ID of Company or Manufacturer.<br>This ID is applied and registered from USB-IF.<br>Refer to this website for applying VID:<br>http://www.usb.org/developers/vendor/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| Product ID (PID)                             | 23E3 (hex)                        | USB Product ID assigned by Manufacturer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| Release No. (BCD)                            | 0100 (hex)                        | This field reports the release number of the USB device chip. This item is not allowed to be modified.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| Device Power Mode                            | Bus Powered (100mA)               | This field sets the USB device if bus-powered or self-powered device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| Max Power 100mA                              |                                   | This field sets the USB device maximum power that<br>can be drawn by the device from the USB host. Enter<br>the value here if it is not 100mA or 500mA. Expressed<br>in 2 mA units (i.e., 50 = 100 mA).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| USB Selective<br>Suspend                     | Enable                            | This field enables/disables the USB Selective Suspend<br>function. When enabled, Windows OS will suspend the<br>device when idle for few seconds (COM port not open).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| Manufacturer String Prolific Technology Inc. |                                   | This field contains the product manufacturer string.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| Product String                               | USB-Serial Controller             | This field when entered will be the device string<br>displayed by Windows and other OS when device is<br>first detected and before driver is loaded or driver not<br>installed. After driver is loaded, Windows will show the<br>product string written inside the driver INF file.                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| Serial Number                                | Enable Unique Serial<br>Number ID | <ul> <li>Disable Serial Number – this option will disable the Serial Number. Operating System will assign a random serial number for the device.</li> <li>Enable Unique Serial Number ID – this default option enables the unique serial number pre-programmed inside the chip.</li> <li>Custom Serial Number – this option allows the customer to set own product serial numbering:         <ul> <li>Auto SN: allows to add prefix while the numbers auto increment after each write.</li> <li>Fixed SN: this will write the same number.</li> </ul> </li> <li>Device with serial number enabled allows the device to be assigned with the same COM port number even when plug to other USB ports of the same PC.</li> </ul> |  |  |  |

NOTE: The total string length for the manufacturer + product + serial number string is up to 90 characters.

## 9.2 UART Configuration

USB UART GPIO\_A GPIO\_B MISC -UART control-UART mode Access LED EED flash fast (11.4 Hz) full-duplex UART C LED flash slow (2.8 Hz) half-duplex UART Remote Wakeup by RXD(UART) Disable C Enable UART flow control settting: Software ( disable software flow control  $\bigcirc$  enable software flow control -UART flow control settting: Hardware ( disable hardware flow control enable RTS/CTS flow control enable DTR/DSR flow control enable RTS/CTS and DTR/DSR flow contro Buffer size and up-stream flow control threshold settings: Down stream / Up stream / High Watermark / Low 256 768 736 C 256 768 640 С 512 512 480  $\odot$ 512 512 448 Help

#### Table 9-2 UART Startup Configuration

| Functions                    | Default Value                          | Description                                                                                                                                                                                                                                                         |

|------------------------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LED Flash                    | Fast                                   | This option sets the flashing speed of the access LED when configured using the TX_LED, RX_LED, TRX_LED GPIO pins. Fast 11.4Hz and slow 2.8Hz.                                                                                                                      |

| UART Mode                    | Full-duplex UART                       | <ul> <li>Full-Duplex UART - this default setting allows simultaneous transmission of TX and RX lines.</li> <li>Half-Duplex UART - this option only allows for one-way transmission at a time. When there is no data transmission, TXD will be tri-state.</li> </ul> |

| Remote Wakeup (RXD)          | Disable                                | This allows using the RXD pin as remote wakeup.<br>The received data from RXD may be wrong while chip<br>is waking up.                                                                                                                                              |

| Software Flow Control        | Disable                                | This option allows setting the software flow control (Xon/Xoff) during chip initial startup. In general, this option need not enabled because driver or software can control this option.                                                                           |

| Hardware Flow Control        | Disable                                | This option allows setting the hardware flow control (RTS/CTS, DTR/DSR, Both) during chip initial startup. In general, this option need not enabled because driver or software can control this option.                                                             |

| Buffer Size<br>Configuration | 256(TX) - 768(RX)<br>736(HW) - 384(LW) | This sets the internal buffer size configuration for TX (downstream) and RX (upstream) as well as the high and low watermark threshold levels.                                                                                                                      |

# 9.3 GPIO (GPA) Configuration

Also refer to Section 7.4 for the complete GPIO Multi-Function options description.

| USB UART | GPIO_A GPIO_B MISC |                      |                   |                     |                                   |

|----------|--------------------|----------------------|-------------------|---------------------|-----------------------------------|

| GPA0     | IO Function        | enable<br>open-drain | enable<br>pull-up | Inverse<br>Polarity | Outbut<br>driving select<br>4mA 💌 |

| GPA1     | RXD 💌              |                      |                   |                     | 4mA ▼                             |

| GPA2     | RTS                |                      |                   |                     | 4mA 💌                             |

| GPA3     | CTS 💌              |                      |                   |                     | 4mA 💌                             |

| GPA4     |                    |                      |                   |                     | 4mA 💌                             |

| GPA5     | DSR 💌              |                      |                   |                     | 4mA ▼                             |

| GPA6     |                    |                      |                   |                     | 4mA 💌                             |

| GPA7     | RI(WAKEUP)         |                      |                   |                     | 4mA 💌                             |

|          |                    |                      |                   |                     |                                   |

## Table 9-3 GPIO (GPA Group) Configuration

| GPIO Function | Default Value | Default I/O | Description                                                |

|---------------|---------------|-------------|------------------------------------------------------------|

|               |               |             | This field also allows setting the pin as a standard GPIO. |

| GPA0          | TXD           | Output      | TXD (default)                                              |

|               |               |             | GPIO (General Purpose I/O)                                 |

|               |               |             | This field also allows setting the pin as a standard GPIO. |

| GPA1          | RXD           | Input       | RXD (default)                                              |

|               |               |             | GPIO (General Purpose I/O)                                 |

|               |               |             | This field allows setting the pin as a standard GPIO or    |

|               |               |             | any of the following function:                             |

|               |               |             | RTS (default)                                              |

|               |               |             | • TX_LED                                                   |

| GPA2          | RTS           | Output      | CLK_OUT (also refer to MISC folder)                        |

|               |               |             | SUSP_N (also refer to MISC folder)                         |

|               |               |             | USB_CFG                                                    |

|               |               |             | • TXEN                                                     |

|               |               |             | GPIO (General Purpose I/O)                                 |

|               |               |             | This field allows setting the pin as a standard GPIO or    |

|               |               |             | any of the following function:                             |

| GPA3          | CTS.          | lanut       | CTS (default)                                              |

| GPAS          | CTS           | Input       | • RX_LED                                                   |

|               |               |             | • TRX_LED                                                  |

|               |               |             | WAKEUP                                                     |

# Product Data Sheet PL2303GE

| <b></b>                         |             |        | 1                                                                                      |  |  |

|---------------------------------|-------------|--------|----------------------------------------------------------------------------------------|--|--|

|                                 |             |        | <ul> <li>VBUS_DET (also refer to MISC folder)</li> <li>BC_DET</li> </ul>               |  |  |

|                                 |             |        | GPIO (General Purpose I/O)                                                             |  |  |

|                                 |             |        | This field allows setting the pin as a standard GPIO or any of the following function: |  |  |

|                                 |             |        | DTR (default)                                                                          |  |  |

|                                 |             | _      | • TX_LED                                                                               |  |  |

| GPA4                            | DTR         | Output | CLK_OUT (also refer to MISC folder)                                                    |  |  |

|                                 |             |        | • USB_CFG                                                                              |  |  |

|                                 |             |        | • EE SDA                                                                               |  |  |

|                                 |             |        | GPIO (General Purpose I/O)                                                             |  |  |

|                                 |             |        | This field allows setting the pin as a standard GPIO or                                |  |  |

|                                 |             |        | any of the following function:                                                         |  |  |

|                                 |             |        | DSR (default)                                                                          |  |  |

|                                 |             | Input  | • RX_LED                                                                               |  |  |

| GPA5                            | DSR         |        | • TRX_LED                                                                              |  |  |

|                                 |             |        | • BC_SUSP_N                                                                            |  |  |

|                                 |             |        | • EE SCL                                                                               |  |  |

|                                 |             |        | GPIO (General Purpose I/O)                                                             |  |  |

|                                 |             |        | This field allows setting the pin as a standard GPIO or                                |  |  |

|                                 |             |        | any of the following function:                                                         |  |  |

|                                 |             |        | DCD (default)                                                                          |  |  |

| GPA6                            | DCD         | Input  | VBUS_DET (also refer to MISC folder)                                                   |  |  |

|                                 |             | mpar   | • BC_DET                                                                               |  |  |

|                                 |             |        | • TXEN                                                                                 |  |  |

|                                 |             |        | GPIO (General Purpose I/O)                                                             |  |  |

|                                 |             |        | This field also allows setting the pin as a standard GPIO.                             |  |  |

| GPA7                            | RI (Wakeup) | Input  | <ul> <li>RI (default)</li> </ul>                                                       |  |  |

| GFA/                            | i (wakeup)  | input  | GPIO (General Purpose I/O)                                                             |  |  |

| Enchio                          |             |        | · · · · ·                                                                              |  |  |

| Enable<br>Open-Drain            | Disal       | bled   | This field sets the selected I/O pin to open-drain output mode.                        |  |  |

|                                 |             |        | This field enables the selected I/O pin weak pull-up.                                  |  |  |

|                                 |             |        | NOTE: The weak pull-up resistor is pull-up to VDD_IO.                                  |  |  |

| Enable-Pull Up                  | Disal       | bled   | When enabling pull-up for input pins, the input signal                                 |  |  |

|                                 |             |        | voltage should not be higher than the VDD_IO voltage.                                  |  |  |

|                                 |             |        | -                                                                                      |  |  |

|                                 | D:          | blad   | This field inverts the selected I/O pin input and output                               |  |  |

| Inverse Polarity                | Disal       | bled   | This field inverts the selected I/O pin input and output signal polarity.              |  |  |

| Inverse Polarity Output Driving | Disal<br>4m |        |                                                                                        |  |  |

# 9.4 GPIO (GPB) Configuration

Also refer to Section 7.4 for the complete GPIO Multi-Function options description.

| USB UART | GPIO_A GPIO_B | MISC |                      |                   |                     |                          |

|----------|---------------|------|----------------------|-------------------|---------------------|--------------------------|

|          | IO Function   |      | enable<br>open-drain | enable<br>pull-up | Inverse<br>Polarity | Outout<br>driving select |

| GPB0     | GPIO          | •    |                      |                   |                     | 4mA ▼                    |

| GPB1     | GPIO          | •    |                      |                   |                     | 4mA ▼                    |

| GPB2     | GPIO          | •    |                      |                   |                     | 4mA 💌                    |