# **Application Note**

# PL-25A1 (Rev B) Hi-Speed USB Host to Host Bridge Controller PCB Layout Guide

#### Introduction

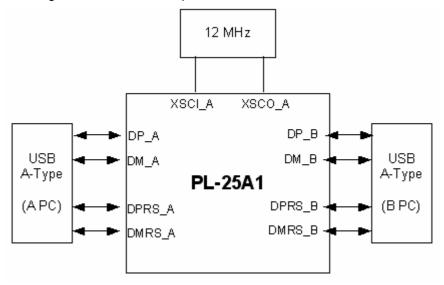

This document explains how to design a PCB for Prolific PL-25A1 (Chip Rev B) Hi-Speed USB Host to Host Bridge Controller device with the following goals in mind:

- 1. Make a noise-free, power-stable environment suitable for the PL-25A1.

- 2. Reduce the possibility of EMI and EMC.

- 3. Simplify the task of routing signal trace to make a better design circuit.

#### **Placement**

The following are the guidelines for an ideal placement:

- The distance between USB\_A-type to PL-25A1 should be as short as possible.

- The distance between the Crystal to PL-25A1 XSCI and XSCO should also be as short as possible.

- Crystal should not be placed near I/O ports, board edges, and other high-frequency devices or traces (such as Power signal) or magnetic field devices (such as magnetic).

- The outer shield of Crystal needs well grounding to prevent EMC/EMI from inducing extra noise. The retaining straps of the Crystal also need well grounding.

- High Current devices should be placed near the Power source to reduce the trace length.

Traces with high current will induce more EMI.

- Route USB 2.0 differential pairs near non-USB 2.0 I/O connectors, signal headers, crystals, oscillators, magnetic devices, and power connectors.

Document Rev 1.0 lg\_pl25A1B\_v1.0.doc

#### **Trace Routing**

Good routing of traces can reduce the propagation delay, cross talk, and high-frequency noise. It can also improve the signal quality for the receiver and reduce the loss from transmitted signals.

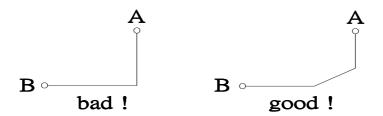

• Avoid right angle signal traces:

- Avoid digital signals that interfere with analog signals (crystal clock) and Power trace.

- The trace length and the ratio of trace width to trace height above the ground planes should be considered carefully. The clocks and other high speed signal traces should be as short and wide as possible (compare with normal digital trace). It is better to have a ground plane under these traces, and if possible, with GND plane around.

- The trace of Power signal should be short and wide.

- User should connect a 10uF and 0.1uF capacitors between REG VO and GND.

- The traces listed below should be wider and short as possible. The traces should also not cross any signal traces.

- The traces between the crystal and XIN, XOUT.

- > The traces between USB connector and DM, DP,

- The traces between the capacitors and REG\_VIN.

- > The traces between the capacitors and REG VO.

- The traces between the capacitors and REG\_GND.

- The trace length between crystal and XSCI, and the trace length between crystal and XSCO should be equal.

- The trace length between USB connector and DM, and the trace length between USB connector and DP should be equal.

# Prolific TECHNOLOGY FOR TOMORROW

### PL-25A1B PCB Layout Guide

Document Rev 1.0 lg\_pl25A1B\_v1.0.doc

#### **Power and Ground Planes**

- 3.3V power: support PL-25A1 and other devices. Avoid using unnecessary power trace to PL-25A1 and keep these traces short and wide.

- GND plane You can separate the digital GND to Analog GND as follows: Partition of GND plane needs experience and experiment. The key point is to keep the return path of analog GND almost the same to the common GND. If you do not feel confident on this, simply leave the GND plane unchanged (i.e. no partition at all).

- For all partition on Power/GND plane, right angle is not recommended. This is the same to the signal/power/bus traces.

### For Better and More Stable Analog Performance

- When using 12MHz crystal as clock source, you should pay more attention to the specification

of crystal. Please refer to the USB crystal spec. When using crystal as specification, two

matching caps (22pF in schematic) should be attached to the XSCI and XSCO pin.

- When using oscillator as clock source (12MHz), avoid attaching any cap on the clock trace.

- GND plane partition is not recommended, please keep the GND plane as large and clear as possible.

- PCB characteristics will have an affect on the reference resistor value (RREF\_A, RREF\_B) of the USB PHY. Please consult Prolific FAE for advice.

Document Rev 1.0 lg\_pl25A1B\_v1.0.doc

#### **Disclaimer**

All the information in this document is subject to change without prior notice. Prolific Technology Inc. does not make any representations or any warranties (implied or otherwise) regarding the accuracy and completeness of this document and shall in no event be liable for any loss of profit or any other commercial damage, including but not limited to special, incidental, consequential, or other damages.

## Copyrights

#### Copyright © 2008 Prolific Technology Inc. All rights reserved.

No part of this document may be reproduced or transmitted in any form by any means without the express written permission of Prolific Technology Inc.

Prolific Technology Inc.

7F, No. 48, Sec. 3, Nan Kang Road

Nan Kang, Taipei 115

Taiwan, R.O.C.

Telephone: +886-2-2654-6363

Fax: +886-2-2654-6161 http://www.prolific.com.tw