# SuperSpeed USB 3.0 Host-to-Host Bridge Controller

Product Data Sheet PL27A1

- SuperSpeed USB 3.0 Host-to-Host Bridge Controller

- ➤ USB 3.0 and USB 2.0 specification compliant

- > Transfer data between two Hosts via USB port

- Supports various transfer protocol modes:

| Product ID (PID) | Protocol (by firmware)      |

|------------------|-----------------------------|

| 27A1             | Trans. cable/WINUSB for     |

|                  | Prolific PClinq5 software   |

| 27A3             | CDC ACM_ Serial device      |

| 27A5             | RNDIS_ Network adapter      |

| 27A7             | Trans. cable/WINUSB for     |

|                  | custom application software |

- WINUSB and CDC/ACM drivers are built in on Windows, Mac OS and Linux(for ACM), An inf file is needed for driver installation on Win7 and 8.1, RNDIS driver is built in on Windows and Linux

- For 27A1 mode, PClinq5 software can be stored in external SPI Flash and implemented by read-only Mass Storage Device on Windows and Mac OS. Available disk capacity is about 12MB.

- Supports external SPI Flash to customize USB vendor/product ID

- QFN64 Package

- USB Device Interface:

- 2 x USB Device PHYs

- Supports 5GHz SuperSpeed, 480MHz Hi-Speed, and 12MHz Full-Speed mode

- One General Purpose SPI Master controller

- USB Endpoint 0 for Control Endpoint with dedicated 512 bytes buffer for each USB

- Highly configurable endpoint structure

- Pass Through Channel FIFO architecture can utilize full USB bandwidth for data transferring

- Provides LED pin for access indicator

- 8-bit High Performance 1T 8032 MCU

- > 3.3V Digital I/O Pad

- > 1.2V Power Supply for Core

- Built-in 5V to 3V linear low-dropout regulator

- Embedded Power on Reset (POR)

- > 30MHz crystal oscillator for both USB PHYs

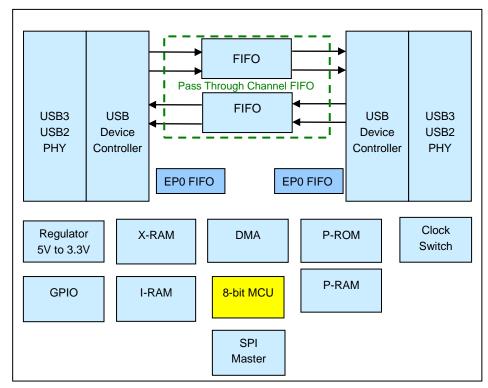

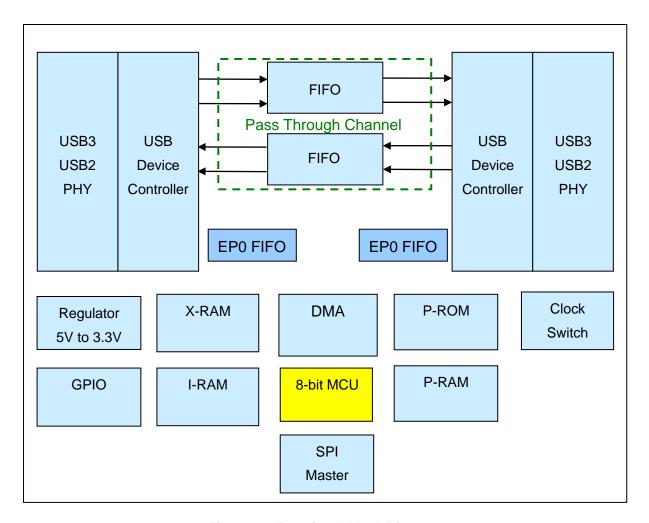

**System Block Diagram**

7F, No.48, Sec. 3, Nan Kang Rd., Nan Kang, Taipei 115, Taiwan

Tel: +886-2-2654-6363; Fax: 886-2-22654-6161

Website: http://www.prolific.com.tw/

# SuperSpeed USB 3.0 Host-to-Host Bridge Controller

**Product Data Sheet** PL27A1

# **Ordering Information**

| Product | Package Type       | Ordering Number |

|---------|--------------------|-----------------|

| PL27A1  | 64-pin QFN (9x9mm) | PL27A1A4FKG7P1  |

**Prolific Technology Inc.**7F, No.48, Sec. 3, Nan Kang Rd., Nan Kang, Taipei 115, Taiwan Tel: +886-2-2654-6363; Fax: 886-2-22654-6161

Website: http://www.prolific.com.tw/

# **Table of Contents**

| Ord | ering | g Information                                 | 2  |

|-----|-------|-----------------------------------------------|----|

| 1.  | Ove   | erview                                        | 5  |

|     | Fea   | tures                                         | 7  |

| 2.  | Fun   | nctional Block Diagram                        | 8  |

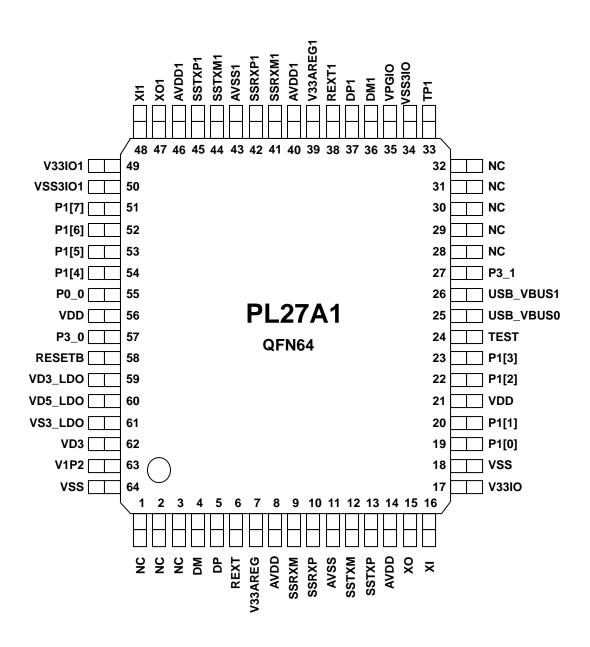

| 3.  | Pin   | Diagram                                       | 9  |

| 4.  |       | Assignment & Description                      |    |

|     | 4.1   | USB0 PHY Related Pins                         | 10 |

|     | 4.2   | USB1 PHY Related Pins                         | 10 |

|     | 4.3   | System Pins                                   | 11 |

| 5.  | Fun   | nctional Description                          | 12 |

|     | 5.1   | USB3 / USB2 PHY                               | 12 |

|     | 5.2   | USB Device Controller                         | 12 |

|     | 5.3   | Pass-Through Channel FIFO                     | 12 |

|     | 5.4   | EP0 FIFO                                      | 12 |

|     | 5.5   | Regulator                                     | 12 |

|     | 5.6   | Clock Switch                                  | 12 |

|     | 5.7   | 8-bit MCU                                     | 12 |

|     | 5.8   | P-ROM                                         | 12 |

|     | 5.9   | 256B I-RAM                                    | 13 |

|     | 5.10  | ) X-RAM                                       | 13 |

|     | 5.11  | GPIO and PWM                                  | 13 |

|     | 5.12  | 2 DMA                                         | 13 |

|     | 5.13  | SPI Flash Controller                          | 13 |

| 6.  | Ele   | ctrical Characteristics                       | 14 |

|     | 6.1   | Absolute Maximum Ratings                      | 14 |

|     | 6.2   | Recommended Operating Conditions              | 14 |

|     | 6.3   | Recommended Operating Conditions of 3.3V GPIO | 14 |

|     | 6.4   | Operating Current                             | 15 |

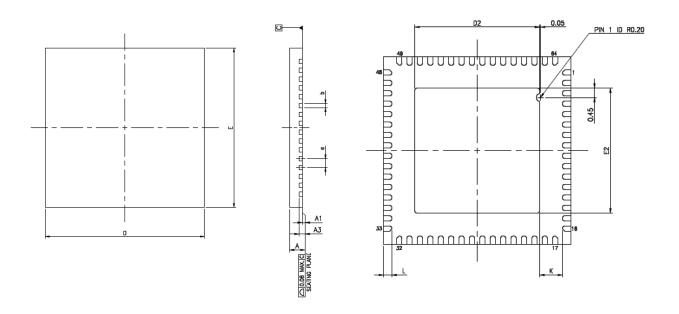

| 7.  | Out   | lline Diagram                                 | 16 |

# **List of Figures**

| Figure 1-1 Target Application (USB 3.0 to USB 3.0 Host Cable) | 5  |

|---------------------------------------------------------------|----|

| Figure 2-1 Functional Block Diagram                           | 8  |

| Figure 3-1 PL27A1 Pin Diagram (QFN64)                         |    |

| Figure 7-1 Outline Diagram of QFN64                           | 16 |

|                                                               |    |

|                                                               |    |

|                                                               |    |

| <u>List of Tables</u>                                         |    |

|                                                               |    |

| Table 4-1 USB0 PHY Related Pins                               | 10 |

| Table 4-2 USB1 PHY Related Pins                               | 10 |

| Table 4-3 System Pins                                         | 11 |

| Table 6-1 Absolute Maximum Ratings                            | 14 |

| Table 6-2 Recommended Operating Conditions                    | 14 |

| Table 6-3 Recommended Operating Conditions of 3.3V GPIO       | 14 |

| Table 6-4 Operating Current                                   | 15 |

## 1. Overview

The PL27A1 is a single-chip SuperSpeed USB 3.0 Host-to-Host bridge controller specially designed for USB host to host data transfer. SuperSpeed USB has data transfer bandwidth of up to 5Gbps offering 10X performance increase over Hi-Speed USB 2.0 (480Mbps). SuperSpeed USB is backward compatible and interoperates with all USB3.0/USB2.0/USB1.1 hosts, devices, and hubs.

Figure 1-1 Target Application (USB 3.0 to USB 3.0 Host Cable)

The PL27A1 chip offers external firmware for various data transfer mode protocols:

| Part<br>Number | External Firmware Function Mode | USB VID/PID (by firmware) | Transfer Cable (WINUSB) | UART<br>(CDC/ACM) | Remote<br>NDIS | Package |

|----------------|---------------------------------|---------------------------|-------------------------|-------------------|----------------|---------|

| PL27A1         | Easy Transfer Cable             | 067B/27A1                 | V                       |                   |                | QFN64   |

| PL27A1         | Serial Device                   | 067B/27A3                 |                         | V                 |                | QFN64   |

| PL27A1         | RNDIS(Network adapter)          | 067B/27A5                 |                         |                   | V              | QFN64   |

| PL27A1         | Custom Transfer Cable           | 067B/27A7                 | V                       |                   |                | QFN64   |

### • 27A1 Mode (USB Easy Transfer Cable):

This mode enumerates the cable as a USB Easy Transfer Cable device using built-in WINUSB driver.

This cable mode is originally designed for Microsoft Windows Easy Transfer (WET) program built inside Windows Vista, Windows 7, and Windows 8 and also available for installation in Windows XP. Using the Windows Easy Transfer program, the PL27A1 USB 3.0 transfer cable allows users to easily connect an old computer running Microsoft Windows XP/Vista/7/8 to another new computer running Windows Vista/7/8 thru the USB ports. Once the program has established connection for both computers, the user can then easily transfer large data files and program settings from the old computer to the new computer. It's the fastest and easiest way to transfer files and program settings from an old Windows PC to a new Windows PC. Users can still use the cable in Windows 8.1 and 10 by copying the old WET program in

Windows 7 or 8.

The PL27A1 also comes with the Prolific PCLinq5 file transfer software for Windows and Mac. PCLinq5 is a versatile user-friendly file manager program that allows the end-user to see and control file directories on both PCs and Macs at the same time. End-users can easily drag-and-drop or cut-and-paste files and folders between remote and local PCs as well as creating new folders and changing file attributes. PCLinq5 supports Windows XP, Vista, 7, 8, and 10 versions as well as Mac OS X latest versions.

### • 27A3 Mode (USB Serial Device):

This mode enumerates the cable as a USB Serial Device with virtual COM port on both ends of the host systems using built-in CDC/ACM driver.

USB Communication Device Class (ACM) driver is built inside Windows 10, Mac OS X, and Linux OS which provides a virtual COM port software interface when the cable device is plugged to the computer. The CDC/ACM driver is also available for installation in Windows 7 or Windows 8 by simple INF driver update. By using Serial COM port terminal programs (like HyperTerminal, TeraTerm or Putty), the 27A3 mode cable allows users to easily transfer data between two computers by simply selecting the assigned COM Port number. Once the serial terminal program has established the virtual COM port connection for both computers, the user can then easily transfer large raw data from one computer to another.

#### 27A5 Mode (Network Adapter/RNDIS):

This mode enumerates the device as a Remote NDIS network device on both ends of the USB host.

Fully compliant to Remote NDIS Specification, users can easily communicate between two PCs by using network TCP/IP protocol. Transfer files quickly from one USB host to another and even build a small network and share Internet connection with other PCs. No need to install network drivers or add-on cards. Users can share programs, files, and peripherals easily.

### • 27A7 Mode (Custom USB Transfer Cable):

This mode enumerates the cable as a custom USB Transfer Cable device using built-in WINUSB driver installed by an inf file on Win7(inf file is not needed on Win8.1 and Win10.)

## TO USB Link Transfer Cable

Users can use the mode to define the custom transferring protocol and develop the custom software to implement normal, audio or video data-transferring with less latency. User can use LibUSB library to control the cable device to transfer data between two Linux PCs.

The PL27A1 chip solution is especially suitable for those who need easy bulk data transfer between two USB hosts - either notebook PC or desktop PC or other USB host systems or devices like SETUP boxes, SmartTVs, smartphones and tablets.

#### **Features**

- SuperSpeed USB 3.0 Host-to-Host Bridge Controller

- USB 3.0 and USB 2.0 specification compliant

- SuperSpeed (5Gbps), Hi-Speed (480Mbps), and Full-Speed (12Mbps)

- Transfer data between two USB Hosts (up to SuperSpeed USB 3.0)

- Supports firmware customization for various transfer protocol modes:

- 27A1 mode WINUSB (Easy Transfer Cable)

- 27A3 mode CDC/ACM (USB Serial Device)

- 27A5 mode RNDIS (Network Cable)

- 27A7 Mode WINUSB (Custom USB Transfer Cable)

- WINUSB and CDC/ACM drivers are built in on Windows, Mac OS and Linux(for ACM), An inf file is needed for driver installation on Win7 and 8.1. RNDIS driver is built in on Windows and Linux

- Easy Transfer Cable fully supports Microsoft Windows Easy Transfer built-in software in Windows Vista, Windows 7, and Windows 8.

- Prolific provides royalty-free PCLinq5 software for Windows XP/7/8/10 (Easy Transfer Cable) and Mac OS.

- Compliant with Remote NDIS Specification. Users can link two PCs thru the USB port using network TCP/IP protocol.

- For 27A1 mode, PClinq5 software can be stored in external SPI Flash and implemented by read-only Mass Storage Device on Windows and Mac OS. Available disk capacity is about 12MB.

- 8-bit high-performance 1T 8032 MCU

- USB device interface

- Two USB device PHYs

- USB endpoint 0 for control endpoint with dedicated 512 bytes buffer for each USB side

- Highly configurable endpoint structure. Each endpoint can be configured as interrupt, bulk, and isochronous endpoint.

- Pass Through Channel FIFO architecture utilize full USB bandwidth for data transfer

- Peripherals

- One SPI Flash Controller for external SPI Serial Flash Memory

- Supports DMA feature between external SPI flash and internal FIFO

- Supports multi-vendor SPI Serial Flash Memory

- > 3.3V Digital I/O Pad and 1.2V power supply for core

- Built-in 5V to 3V linear low-dropout regulator, Bus powered from either USB port

- > Embedded power-on reset (POR)

- > 30MHz crystal oscillator (shared by both USB PHYs)

- Supports external SPI Flash to customize USB vendor/product ID

- Supports LED indicator for connection and transfer status

- QFN64 Package

# 2. Functional Block Diagram

Figure 2-1 Functional Block Diagram

## 3. Pin Diagram

Figure 3-1 PL27A1 Pin Diagram (QFN64)

# 4. Pin Assignment & Description

Pin Type Abbreviation:

I: Input O: Output B: Bidirectional A: Analog P: Power/Ground

## 4.1 USB0 PHY Related Pins

**Table 4-1 USB0 PHY Related Pins**

| Symbol      | Туре | Pin No | Description                                |  |  |

|-------------|------|--------|--------------------------------------------|--|--|

| DM          | В    | 4      | High speed D- signal                       |  |  |

| DP          | В    | 5      | High speed D+ signal                       |  |  |

| REXT        | Α    | 6      | Connect external resistor to analog ground |  |  |

| V33AREG     | Р    | 7      | Analog power 3.3V for on-chip USB 2.0 PHY  |  |  |

| AVDD        | Р    | 8      | Analog power 1.2V for on-chip USB PHY      |  |  |

| SSRXM       | I    | 9      | SuperSpeed RXM signal                      |  |  |

| SSRXP       | 1    | 10     | SuperSpeed RXP signal                      |  |  |

| AVSS        | Р    | 11     | Analog power 3.3V for on-chip USB PHY      |  |  |

| SSTXM       | 0    | 12     | SuperSpeed TXM signal                      |  |  |

| SSTXP       | 0    | 13     | SuperSpeed TXP signal                      |  |  |

| AVDD        | Р    | 14     | Analog power 1.2V for on-chip USB PHY      |  |  |

| XO          | В    | 15     | Crystal oscillator 30MHz clock output      |  |  |

| XI          | I    | 16     | Crystal oscillator 30MHz clock input       |  |  |

| AVDD3/V33IO | Р    | 17     | Analog power 3.3V for on-chip USB PHY      |  |  |

## 4.2 USB1 PHY Related Pins

**Table 4-2 USB1 PHY Related Pins**

| Symbol        | Туре | Pin No | Description                                |  |  |

|---------------|------|--------|--------------------------------------------|--|--|

| DM1           | В    | 36     | High speed D- signal                       |  |  |

| DP1           | В    | 37     | High speed D+ signal                       |  |  |

| REXT1         | Α    | 38     | Connect external resistor to analog ground |  |  |

| V33AREG1      | Р    | 39     | Analog power 3.3V for on-chip USB 2.0 PHY  |  |  |

| AVDD1         | Α    | 40     | Analog power 1.2V for on-chip USB PHY      |  |  |

| SSRXM1        |      | 41     | SuperSpeed RXM signal                      |  |  |

| SSRXP1        |      | 42     | SuperSpeed RXP signal                      |  |  |

| AVSS1         | Р    | 43     | Analog power 3.3V for on-chip USB PHY      |  |  |

| SSTXM1        | 0    | 44     | SuperSpeed TXM signal                      |  |  |

| SSTXP1        | 0    | 45     | SuperSpeed TXP signal                      |  |  |

| AVDD1         | Р    | 46     | Analog power 1.2V for on-chip USB PHY      |  |  |

| XO1           | В    | 47     | Crystal oscillator 30MHz clock output      |  |  |

| XI1           | I    | 48     | Crystal oscillator 30MHz clock input       |  |  |

| AVDD31/V33IO1 | Р    | 49     | Analog power 3.3V for on-chip USB PHY      |  |  |

# 4.3 System Pins

**Table 4-3 System Pins**

| Symbol    | Туре | Pin No | Description                                             |  |

|-----------|------|--------|---------------------------------------------------------|--|

| VSS3IO    | Р    | 18     | 3.3V I/O ground                                         |  |

| P1[0]     | В    | 19     | LED_TRAN: P1[0] - Control pin for LED behavior during   |  |

| F I[O]    | ь    | 19     | data transfer operation of relative USB side.           |  |

| P1[1]     | В    | 20     | LED_TRAN: P1[1] – Control pin for LED behavior during   |  |

| ן ין י    |      | 20     | data transfer operation of relative USB side.           |  |

| VDD       | Р    | 21     | 1.2V core power                                         |  |

| P1[2]     | В    | 22     | GPIO P1[2]                                              |  |

| P1[3]     | В    | 23     | GPIO P1[3]                                              |  |

| TEST      | ļ    | 24     | Chip Test mode enable. Must be NC or tied to Ground.    |  |

| USB_VBUS0 | I    | 25     | USB power signal from side 0 USB VBUS                   |  |

| USB_VBUS1 | I    | 26     | USB power signal from side 1 USB VBUS                   |  |

| D2 4      | В    | 27     | LED_indicator: Control pin for single LED mode during   |  |

| P3_1      | Ь    | 21     | any side data transfer operation.                       |  |

| TP1       |      | 33     | Must be pulled down(4.7KΩ) to GND.                      |  |

| VSS3IO    | Р    | 34     | 3.3V I/O ground                                         |  |

| VPGIO     | Р    | 35     | 3.3V Power pin                                          |  |

| VSS3IO1   | Р    | 50     | 3.3V I/O ground                                         |  |

| P1[7]     | В    | 51     | Must be floating if not used.                           |  |

| P1[6]     | В    | 52     | Must be floating if not used.                           |  |

| P1[5]     | В    | 53     | Serial Flash Data Output. Must be floating if not used. |  |

| P1[4]     | В    | 54     | Serial Flash Data Input. Must be floating if not used.  |  |

| P0[0]     | В    | 55     | Serial Flash Clock Input. Must be floating if not used. |  |

| VDD       | Р    | 56     | 1.2V Core Power                                         |  |

| P3_0      | В    | 57     | Serial Flash Chip Select. Must be floating if not used. |  |

| RESETB    | I    | 58     | External reset pin, active low                          |  |

| VD3_LDO   | Р    | 59     | 3.3V LDO regulator output voltage                       |  |

| VD5_LDO   | Р    | 60     | 5V LDO regulator input voltage                          |  |

| VS3_LDO   | Р    | 61     | Ground of LDO                                           |  |

| VD3       | Р    | 62     | 3.3V regulator input voltage (from LDO output)          |  |

| V1P2      | Р    | 63     | 1.2V Power Input                                        |  |

| VSS       | Р    | 64     | Ground                                                  |  |

| NO        | ſ    | 1,2,3, | ,3, No Connection. Keep floating.                       |  |

| NC        | В    | 28~32  | _                                                       |  |

## 5. Functional Description

### 5.1 **USB3 / USB2 PHY**

The USB physical layer IP generates and responds USB electrical signals. These two USB physical layers IP comply with USB 3.0 and USB 2.0 specification. The USB 3.0 part uses PIPE interface to communicate with USB 3.0 controller while the USB 2.0 part uses UTMI interface to communicate with USB 2.0 controller.

### 5.2 USB Device Controller

The USB device controller generates and decodes USB transactions including packet header, CRC check, data payload, etc. This controller acts as USB device that can accept host transaction and responds data or status. Each USB device controller has dedicated control endpoint FIFO to handle USB SETUP token and its data transfer.

## 5.3 Pass-Through Channel FIFO

The Pass-Through Channel FIFO can be used to transfer data packet between two USB controllers side. When the data packet is inputted from one USB side, the other side can output it directly. There are two pairs (IN and OUT) pass-through channels in this chip.

#### **5.4 EP0 FIFO**

The EP0 FIFO is used to endpoint 0 transfer data packet only for each side and the size is a maximum packet size of every USB speed mode.

## 5.5 Regulator

The Regulator IP is included to generate IO 3.3V supply voltage.

### 5.6 Clock Switch

Clock switch is designed to handle clock switch between two sides USB at attach/detach and suspend/resume state.

### 5.7 8-bit MCU

This chip uses high performance 1T 8032 8-bit microcontroller. It provides higher performance than general 8032 MCU.

## 5.8 P-ROM

There is a Program ROM in this chip. After power on reset, the MCU of this chip runs program from this Program ROM (P-ROM).

### 5.9 256B I-RAM

256 bytes IDATA RAM for 8032 MCU. This memory space can provide high speed scratchpad memory for MCU.

#### 5.10 X-RAM

XDATA RAM for 8032 MCU. This is MCU data memory located at XDATA space and MCU uses it to store data in process.

#### 5.11 GPIO and PWM

Two PWM signal generators which can be used to control LED flashing behavior. There are also some GPIO signals that can be controlled directly by MCU. These signals are multiplexed with peripherals. If some peripherals are turned on, the GPIO signals which is multiplexed will be disabled and these signals change to peripheral signals.

### 5.12 DMA

The DMA controller is used to transfer data between FIFO XDATA RAM and peripherals. MCU can control this DMA to get data from FIFO or to put data to FIFO from XDATA RAM. It can also be used to transfer data between P-RAM to SPI flash controller or eMMC flash controller.

### 5.13 SPI Flash Controller

SPI Flash Controller can be used to access data of SPI serial flash memory. The SPI clock rate can be adjusted by MCU.

## 6. Electrical Characteristics

## 6.1 Absolute Maximum Ratings

**Table 6-1 Absolute Maximum Ratings**

| SYMBOL                                           | PARAMETER                 | RATING             | UNITS    |

|--------------------------------------------------|---------------------------|--------------------|----------|

| Vсск                                             | 1.2V Core Power Supply    | -0.3 to 1.4        | V        |

| Vcc                                              | 3.3V Power Supply         | -0.3 to 4.0        | <b>V</b> |

| V <sub>D5</sub>                                  | 5V Power Supply           | oly -0.3 to 6.0    |          |

| Vous                                             | Input Voltage of 3.3V I/O | -0.3 to Vcc3I +0.3 | V        |

| VIN3 Input Voltage of 3.3V I/O with 5V Tolerance |                           | -0.3 to 5.5        | V        |

| T <sub>STG</sub>                                 | Storage Temperature       | -40 to 150         | °C       |

## 6.2 Recommended Operating Conditions

**Table 6-2 Recommended Operating Conditions**

| SYMBOL          | PARAMETER                | MIN  | TYP | MAX  | UNITS |

|-----------------|--------------------------|------|-----|------|-------|

| V <sub>D5</sub> | 5V Power Supply          | 4.5  | 5   | 5.5  | V     |

| Vсск            | 1.2V Core Power Supply   | 1.14 | 1.2 | 1.31 | V     |

| Vcc3i           | Power Supply of 3.3V I/O | 3.0  | 3.3 | 3.6  | V     |

| Т               | Operating Temperature    | 0    | 25  | 70   | °C    |

## 6.3 Recommended Operating Conditions of 3.3V GPIO

**Table 6-3 Recommended Operating Conditions of 3.3V GPIO**

| SYMBOL          | PARAMETER                 | MIN  | TYP | MAX | UNITS |

|-----------------|---------------------------|------|-----|-----|-------|

| VDD33           | I/O Supply Voltage        | 3.0  | 3.3 | 3.6 | V     |

| ViH             | Input High Voltage        | 2.0  |     | 5.5 | V     |

| VIL             | Input Low Voltage         | -0.3 |     | 0.8 | V     |

| R <sub>PU</sub> | Pull-up Resistor          | 62   | 77  | 112 | kΩ    |

| VoL             | Output Low Voltage        |      |     | 0.4 | V     |

| Vон             | Output High Voltage       | 2.4  |     |     | V     |

| I.a.            | Low Level Output Current  | 8    |     |     | mΛ    |

| loL             | @ <b>Vo</b> L =0.4V       | 0    |     |     | mA    |

| lau             | High Level Output Current | 12   |     |     | mA    |

| Іон             | <b>@Vo</b> L =2.4V        | 12   |     |     | IIIA  |

# 6.4 Operating Current

**Table 6-4 Operating Current**

| Symbol | Parameter            | Connection | Current of 3.3V | Current of 1.2V | Units |

|--------|----------------------|------------|-----------------|-----------------|-------|

| IDD    | Operating Current    | USB 3.0    | 57              | 251             | mA    |

|        |                      | USB 2.0    | 41              | 85              | mA    |

|        | Suspend Current      | USB 3.0    | 0.6             | 0.8             | mA    |

| Isus   | (Sleep, bus-powered) | USB 2.0    | 0.9             | 0.65            | mA    |

## 7. Outline Diagram

|               | PACKAGE TYPE |           |      |  |  |  |  |

|---------------|--------------|-----------|------|--|--|--|--|

| JEDEC OUTLINE | MO-220       |           |      |  |  |  |  |

| PKG CODE      | VQFN (Y964)  |           |      |  |  |  |  |

| SYMBOLS       | MIN.         | MIN. NOM. |      |  |  |  |  |

| Α             | 0.80         | 0.85      | 0.90 |  |  |  |  |

| A1            | 0.00         | 0.02      | 0.05 |  |  |  |  |

| А3            | 0.203 REF.   |           |      |  |  |  |  |

| В             | 0.18         | 0.25      | 0.30 |  |  |  |  |

| D             | 9.00 BSC     |           |      |  |  |  |  |

| Е             | 9.00 BSC     |           |      |  |  |  |  |

| е             | 0.50 BSC     |           |      |  |  |  |  |

| K             | 0.20         | -         | -    |  |  |  |  |

|             | E2   |      | D2   |      | L    |      | LEAD FINISH |      | IEDEC CODE |          |     |            |

|-------------|------|------|------|------|------|------|-------------|------|------------|----------|-----|------------|

| PAD SIZE    | MIN. | NOM. | MAX. | MIN. | NOM. | MAX. | MIN.        | NOM. | MAX.       | Pure Tin | PPF | JEDEC CODE |

| 244x244 MIL | 5.90 | 6.00 | 6.05 | 5.90 | 6.00 | 6.05 | 0.35        | 0.40 | 0.45       | V        | Χ   | (V) WMMD-4 |

### NOTES:

- 1. All dimensions are in millimeters.

- 2. Dimension b applies to metallized terminal and is measured between 0.15mm and 0.30mm from the terminal tip. If the terminal has the optional radius on the other end of the terminal, the dimension b should not be measured in that radius area.

- 3. Bilateral coplanarity zone applies to the exposed heat sink slug as well as the terminals.

Figure 7-1 Outline Diagram of QFN64

## **Disclaimer**

All the information in this document is subject to change without prior notice. Prolific Technology Inc. does not make any representations or any warranties (implied or otherwise) regarding the accuracy and completeness of this document and shall in no event be liable for any loss of profit or any other commercial damage, including but not limited to special, incidental, consequential, or other damages.

## **Trademarks**

The Prolific logo is a registered trademark of Prolific Technology Inc. All brand names and product names used in this document are trademarks or registered trademarks of their respective holders.

## Copyrights

Copyright © 2013-2020 Prolific Technology Inc. All rights reserved.

No part of this document may be reproduced or transmitted in any form by any means without the express written permission of Prolific Technology Inc.